## Correlated level shifting technique with cross-coupled gain-enhancement capacitors

## T. Musah and U.-K. Moon

A new technique is proposed to compensate for the loop gain degradation in correlated level shifting. The technique allows the use of a simple single-stage opamp with low gain to realise high effective loop gain. The effect of gain variations on the performance of the proposed correlated level shifting technique is discussed.

*Introduction:* The scaling of process technology has enabled the design of low-power, high-speed digital signal processing blocks. However, analogue circuits have seen reductions in both intrinsic gain and available swing. The correlated double sampling (CDS) technique proposed in [1] provides gain enhancement at the cost of noise power and speed. A parallel correlated double sampling (PCDS) technique presented later in [2] avoids the noise power penalty of CDS. However, both techniques do not allow for high signal swing since they are limited by headroom considerations. The correlated level shifting (CLS) [3] technique offers a solution to both the gain and the swing limitation. However, a level shifting capacitor, used to maintain the opamp output swing low, causes a reduction in loop gain. The proposed CLS scheme employs cross-coupling capacitors to greatly enhance the effective loop gain in the presence of the level-shifting capacitor.

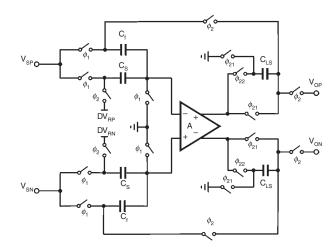

Fig. 1 Correlated level shifting MDAC

Improved correlated level shifting technique: Fig. 1 shows a realisation of the CLS technique in a multiplying digital-to-analogue converter (MDAC). The MDAC is configured for a 1.5 bit pipeline stage. The input signal (V<sub>S</sub>) is sampled onto C<sub>s</sub> and C<sub>f</sub> during  $\phi_1$ . The amplification phase,  $\phi_2$ , is split into two phases:  $\phi_{21}$  for estimation and  $\phi_{22}$  for level shifting and amplification. The level shift capacitor C<sub>LS</sub> samples the estimated output voltage at the end of  $\phi_{21}$ , and is placed in series with the opamp output during  $\phi_{22}$ . This brings the opamp output back to the common-mode voltage, forcing a more accurate virtual ground. During  $\phi_{22}$ , there is charge sharing between C<sub>LS</sub> and the total load capacitance (C<sub>LD</sub>). This degrades the loop gain and causes a nonzero swing at the opamp output in  $\phi_{22}$ . The smaller the capacitance of C<sub>LS</sub>, the worse the loop gain and the larger the opamp output swing in  $\phi_{22}$ . The output voltage at the end of  $\phi_{22}$  is

$$\mathbf{V}_{o} = \left(\frac{C_{s} + C_{f}}{C_{f}}\right) \left[1 \quad \frac{1 + \lambda}{(1 + A_{21}\beta)(1 + A_{22}\beta + \lambda)}\right] V_{S}$$

where

$$\beta = \underbrace{C_f}_{C_s + C_f}, \quad \lambda = \underbrace{C_{LD}}_{C_{LS}}$$

The change in the opamp DC gain from high swing operation in  $\phi_{21}$  to low swing operation in  $\phi_{22}$  is captured in the gain parameters  $A_{21}$  and  $A_{22}$ . For an infinitely large  $C_{LS}$ ,  $\lambda$  is zero and the effective loop gain is a product of the loop gains in  $\phi_{21}$  and  $\phi_{22}$ . A realistic design with  $C_{LS} = C_{LD}$  yields  $\lambda = 1$  and about 6 dB loss in effective loop gain. However, this implies doubling the total load capacitance during  $\phi_{21}$ , thus increasing the power or reducing the speed of the MDAC. The charge sharing between  $C_{LS}$  and  $C_{LD}$  could be reduced if a two-stage opamp is used [3]. This is because the compensation capacitor provides some of the charge needed at the output. However, a two-stage opamp is not always desired for low power submicron realisations and the value of the compensation capacitor is determined by phase margin requirements.

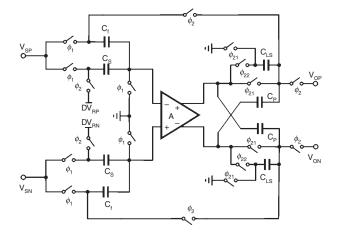

Fig. 2 Correlated level shifting MDAC with improved gain

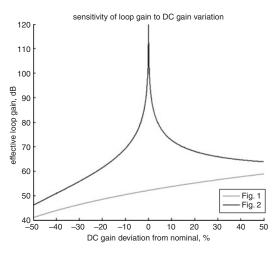

Fig. 3 Effect of DC gain variation on effective loop gain

A CLS MDAC that uses a single-stage opamp and does not suffer from loop gain degradation is shown in Fig. 2. At the end of  $\phi_{21}$ , while the output voltage is sampled on C<sub>LS</sub>, the differential output voltage is held across C<sub>P</sub>. The extra charge needed at the output for a more accurate virtual ground is provided through C<sub>P</sub> and C<sub>LS</sub>. Proper sizing of C<sub>P</sub> allows its use to provide all the charge needed at the output. All the charge injected into (drawn from) C<sub>P</sub> is drawn from (injected into) C<sub>LD</sub>. The output voltage at the end of  $\phi_{22}$  now becomes

$$\mathbf{V}_{o} = \left(\frac{C_{s} + C_{f}}{C_{f}}\right) \left[1 \quad \frac{1 + \lambda}{(1 + A_{21}\beta)(1 + A_{22}\beta + \lambda)}\right] V_{S}$$

where

$$\lambda = \underbrace{\frac{C_{LD} \quad C_P(A_{21}\beta \quad 1)}{C_{LS}}}_{C_{LS}} \leftarrow$$

It is obvious from the above expression that designing for  $\lambda = -1$  will result in an MDAC with no gain error (infinite effective loop gain). Since the value  $\lambda$  is dependent on the opamp DC gain in  $\phi_{21}$ , the designer will need to precisely know the value of  $A_{21}$  to accurately choose C<sub>P</sub>. The sensitivity of the effective loop gain to DC gain deviations from its nominal value due to process and device mismatch is shown in Fig. 3. For the plot, we used an open loop DC gain of 36 dB and assumed it does not change between  $\phi_{21}$  and  $\phi_{22}$ . Also, C<sub>LD</sub> = 800 fF, C<sub>LS</sub> = 440 fF and C<sub>P</sub> = 40 fF. The effective loop gain of the proposed CLS MDAC of Fig. 2 is at least doubled (in dB) as long as the gain deviation from the nominal is less than 20%. This

ELECTRONICS LETTERS 18th June 2009 Vol. 45 No. 13

range will be further widened when the higher  $A_{22}$  is factored into the effective loop gain plot. Although the effective loop gain of the original CLS MDAC of Fig. 1 is less sensitive to DC gain deviations, it remains lower than that of Fig. 2 for any DC gain value.

*Offset and noise performance:* There is an additional kT/C noise power added by the level shifting network. However, since the network is at the output of the MDAC, any noise from it is attenuated by the loop gain. Therefore, the extra noise due to the level shifting network is not significant. However, offset is not attenuated and it sees the same gain to the output as the input signal. The offset and flicker noise could be compensated for by other design techniques for narrowband applications where they limit performance.

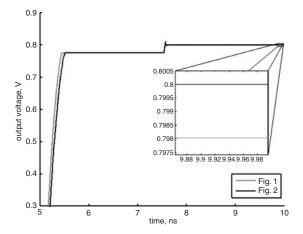

Simulation results: Simulations were run to compare the settling accuracy of the improved CLS MDAC of Fig. 2 with the CLS MDAC of Fig. 1 using identical opamps with 36 dB open loop DC gain. The same capacitance values were used in both MDACs and C<sub>P</sub>, 40 fF. The result is shown in Fig. 4 for the amplification phase,  $\phi_2$ , when a 100 MHz clock is used. The jump at the beginning of  $\phi_{22}$  is due to injection of the corrective charge at the output by C<sub>P</sub>. The height of the jump depends on the size of the load capacitance compared to the output capacitance [3]. As expected, the settling accuracy at the end of  $\phi_{21}$  (7.5 ns) is the same for both circuits, and corresponds to a loop gain of 30 dB. Also, the CLS MDAC of Fig. 1 settles slightly faster in  $\phi_{21}$  because the total load capacitance is less. However, the improved CLS MDAC of Fig. 2 achieves higher than 100 dB effective loop gain at the end of  $\phi_2$ .

Fig. 4 Simulated settling response of proposed CLS MDAC to 400 mV input step (800 mV ideal output)

*Conclusion:* An improved correlated level shifting technique has been proposed. It avoids charge sharing between the level shifting capacitor and the capacitance at the output, hence enhancing the loop gain. The technique has been presented using an MDAC for pipeline/algorithmic ADCs, but is applicable to any other switch capacitor applications such as integrators and biquads.

Acknowledgment: This work is supported by the Semiconductor Research Corporation under contract 2008-HJ-1803.

${\rm (\!C\!\!\!\!C\!\!}$  The Institution of Engineering and Technology 2009

*21 January 2009* doi: 10.1049/e1.2009.0208

T. Musah and U.-K. Moon (School of Electrical Engineering and Computer Science, Oregon State University, 1148 Kelley Engineering Center, Corvallis, OR 97331-5501, USA)

E-mail: musah@eecs.oregonstate.edu

## References

- Nagaraj, K., Viswanathan, T.R., Singhal, K., and Vlach, J.: 'Switchcapacitor circuits with reduced sensitivity to amplifier gain', *IEEE Trans. Circuits Syst.*, 1987, CAS-34, (5), pp. 571–574

- Musah, T., Gregoire, B.R., Naviasky, E., and Moon, U.: 'Parallel correlated double sampling technique for pipelined analogue-to-digital converters', *Electron. Lett.*, 2007, 43, (23), pp. 1260–1261

Gregoire, B.R., and Moon, U.: 'An over-60 dB true rail-to-rail

- 3 Gregoire, B.R., and Moon, U.: 'An over-60 dB true rail-to-rail performance using correlated level shifting and an opamp with only 30 dB loop gain', *IEEE J. Soild-State Circuits*, 2008, **43**, (12), pp. 2620–2630